## 1 Short Answer

Each question is worth 6 points.

1. Construct the truth tale for both the half adder and the full adder. Also, give their logical equations.

Solution:

| Half-Adde |

|-----------|

|-----------|

| a | b | s | c |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

$$s = a'b + ab'$$

$c = ab$

### Full-Adder

| a | b | $c_{in}$ | s | $c_{out}$ |

|---|---|----------|---|-----------|

| 0 | 0 | 0        | 0 | 0         |

| 0 | 0 | 1        | 1 | 0         |

| 0 | 1 | 0        | 1 | 0         |

| 0 | 1 | 1        | 0 | 1         |

| 1 | 0 | 1        | 1 | 0         |

| 1 | 0 | 0        | 0 | 1         |

| 1 | 1 | 1        | 0 | 1         |

| 1 | 1 | 0        | 1 | 1         |

$s = c'_{in}a'b + c'_{in}ab' + c_{in}a'b' + c_{in}ab \qquad c_{out} = c'_{in}ab + c_{in}a'b + c_{in}ab' + c_{in}ab = ab + c_{in}a + c_{in}b' + c_{in}ab = ab + c_{in}a + c_{in}b' + c_{in}ab' + c_{in}ab'$

2. Explain what an encoder circuit does. That is, what are the inputs, outputs, and function.

**Solution:** There are  $2^n$  inputs and n outputs. Which input channel is 1 generates a binary representation of that channel number for the output. So if channel 5 is a 1 then the output would be 101.

3. Explain what a decoder circuit does. That is, what are the inputs, outputs, and function.

**Solution:** There are n inputs and  $2^n$  outputs. The inputs are considered as a single binary number and the value of that number is the single output channel that will be 1, all other output channels will be 0. So of the input is 101, then output channel 5 will be a 1 and all others will be 0.

4. Explain what a multiplexer circuit does. That is, what are the inputs, outputs, and function.

**Solution:** There are  $2^n$  input channels, one output channel, and n control signals. The control signals are considered as a single binary number and the value of that number is the input channel that will be sent to the output channel. So of the control signals are 101, then output will be the same as the input from channel 5.

5. Explain what a demultiplexer circuit does. That is, what are the inputs, outputs, and function.

**Solution:** There are  $2^n$  output channels, one input channel, and n control signals. The control signals are considered as a single binary number and the value of that number is the output channel that will be given the same value as the input channel. So if the control signals are 101, then output channel 5 will be the same as the input.

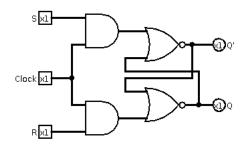

6. Draw the circuit diagram for a clocked SR flip-flop.

### Solution:

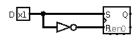

Using a clocked SR flip-flop, draw the diagram for a D flip-flop.

Solution:

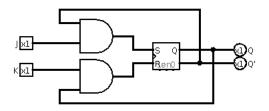

Using a clocked SR flip-flop, draw the diagram for a JK flip-flop.

Solution:

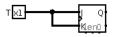

9. Using a clocked JK flip-flop, draw the diagram for a T flip-flop.Solution:

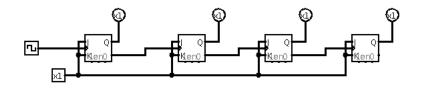

10. Using clocked JK flip-flops, construct a 4-bit counter.Solution:

# 2 Circuit Analysis

Do only one exercise in this section, it is worth 50 points.

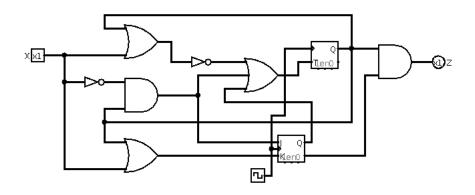

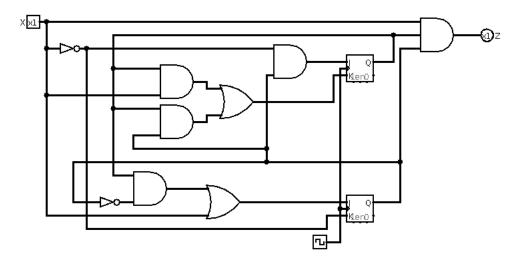

- 11. For the following circuit, the top flip-flop is a T flip-flop and the bottom flip-flop is a JK flip-flop.

- (a) Create the transition tables for the two flip-flops.

- (b) Create the transition table.

- (c) Create the next state table.

- (d) Create the output table.

- (e) Create the next state/output table.

- (f) Create the state diagram.

### Solution:

T flip-flop  $(y_1)$ :  $T = (x + y_1)' + y_2 + x'y_1 = x' + y_2$

| Input Table |   |   |   |  |  |  |

|-------------|---|---|---|--|--|--|

| X           |   |   |   |  |  |  |

| $y_1y_2$    | 0 | 1 |   |  |  |  |

| 00          | 1 | 0 |   |  |  |  |

| 01          | 1 | 1 | - |  |  |  |

| 10          | 1 | 0 |   |  |  |  |

| 11          | 1 | 1 |   |  |  |  |

|          | Х |   |  |  |

|----------|---|---|--|--|

| $y_1y_2$ | 0 | 1 |  |  |

| 00       | 1 | 0 |  |  |

| 01       | 1 | 1 |  |  |

| 10       | 0 | 1 |  |  |

| 11       | 0 | 0 |  |  |

Transition Table

JK flip-flop  $(y_2)$ :  $J = x'y_1$   $K = x + y_1$

| Input T  | Table      | for J | Input     | Tab | ole f | or K | Input     | Tabl | e for | JK | Transi    | tion | і Та | ble |

|----------|------------|-------|-----------|-----|-------|------|-----------|------|-------|----|-----------|------|------|-----|

|          | Х          |       |           | 2   | Χ     |      |           | 2    | Κ     |    |           | 2    | ζ    |     |

| $y_1y_2$ | $0 \mid 1$ |       | $y_1 y_2$ | 0   | 1     | ]    | $y_1 y_2$ | 0    | 1     |    | $y_1 y_2$ | 0    | 1    |     |

| 00       | 0 0        | )     | 00        | 0   | 1     | ]    | 00        | 00   | 01    |    | 00        | 0    | 0    |     |

| 01       | 0 0        | )     | 01        | 0   | 1     | ]    | 01        | 00   | 01    |    | 01        | 1    | 0    |     |

| 10       | 1 (        | )     | 10        | 1   | 1     |      | 10        | 11   | 01    |    | 10        | 1    | 0    |     |

| 11       | 1 (        | )     | 11        | 1   | 1     | ]    | 11        | 11   | 01    |    | 11        | 0    | 0    |     |

|          |            |       |           |     |       | -    |           |      |       |    |           |      |      |     |

| Circuit  | Tab        | les   |           |     |       |      |           |      |       |    |           |      |      |     |

State Transition Ta- Next State Table ble

|           | Х  |    |  |

|-----------|----|----|--|

| $y_1 y_2$ | 0  | 1  |  |

| 00        | 10 | 00 |  |

| 01        | 11 | 10 |  |

| 10        | 01 | 10 |  |

| 11        | 00 | 00 |  |

|           | X |   |  |  |

|-----------|---|---|--|--|

| $y_1 y_2$ | 0 | 1 |  |  |

| 00        | 0 | 0 |  |  |

| 01        | 0 | 0 |  |  |

| 10        | 1 | 1 |  |  |

| 11        | 0 | 0 |  |  |

Output Table

Next State/Output Table

|   | Х   |     |  |  |  |

|---|-----|-----|--|--|--|

|   | 0   | 1   |  |  |  |

| А | C/0 | A/0 |  |  |  |

| В | D/0 | C/0 |  |  |  |

| С | B/1 | C/1 |  |  |  |

| D | A/0 | A/0 |  |  |  |

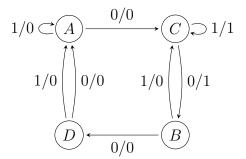

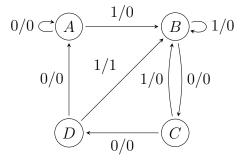

State Diagram

12. Design a sequential circuit that detects an input sequence of 1001 with overlap. Use only JK flip-flops in your construction.

### Solution:

State Diagram

Circuit Tables

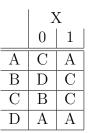

Next State/Output Next State Table Table

|   | Х   |     |  |  |  |

|---|-----|-----|--|--|--|

|   | 0   | 1   |  |  |  |

| А | A/0 | B/0 |  |  |  |

| В | C/0 | B/0 |  |  |  |

| С | D/0 | B/0 |  |  |  |

| D | A/0 | B/1 |  |  |  |

|   |     |     |  |  |  |

|   | Х |   |  |

|---|---|---|--|

| _ | 0 | 1 |  |

| Α | А | В |  |

| В | С | В |  |

| С | D | В |  |

| D | А | В |  |

| ble      |    |    |  |  |

|----------|----|----|--|--|

|          | X  |    |  |  |

| $y_1y_2$ | 0  | 1  |  |  |

| 00       | 00 | 01 |  |  |

| 01       | 10 | 01 |  |  |

| 10       | 11 | 01 |  |  |

| 11       | 00 | 01 |  |  |

State Transition Ta- Output Table

| $Z = xy_1y_2$ |   |   |

|---------------|---|---|

|               | 2 | Κ |

| $y_1 y_2$     | 0 | 1 |

| 00            | 0 | 0 |

| 01            | 0 | 0 |

| 10            | 0 | 0 |

| 11            | 0 | 1 |

JK flip-flop  $(y_1)$ :  $J_1 = x'y_2$   $K_1 = y_1x + y_1y_2$

Transition Table

Input Table for JK Input Table for J

Input Table for K

|              | 2 | Κ |

|--------------|---|---|

| $y_{1}y_{2}$ | 0 | 1 |

| 00           | 0 | 0 |

| 01           | 1 | 0 |

| 10           | 1 | 0 |

| 11           | 0 | 0 |

|              | Х  |    |  |

|--------------|----|----|--|

| $y_{1}y_{2}$ | 0  | 1  |  |

| 00           | 0d | 0d |  |

| 01           | 1d | 0d |  |

| 10           | d0 | d1 |  |

| 11           | d1 | d1 |  |

|              |    |    |  |

|       | X |   |

|-------|---|---|

| $y_2$ | 0 | 1 |

| )0    | 0 | 0 |

| )1    | 1 | 0 |

| .0    | d | d |

| .1    | d | d |

|       |   |   |

| Σ |   |  |

|---|---|--|

| 0 | 1 |  |

| 0 | 0 |  |

| 1 | 0 |  |

| d | d |  |

| d | d |  |

|   |   |  |

|           | X |   |

|-----------|---|---|

| $y_1 y_2$ | 0 | 1 |

| 00        | d | d |

| 01        | d | d |

| 10        | 0 | 1 |

| 11        | 1 | 1 |

JK flip-flop  $(y_2)$ :  $J_2 = x + y_1 y'_2$  $K_2 = x'$

| Transition Table |

|------------------|

|------------------|

Х 1 0  $y_1 y_2$ 00 0d1d d101d010 1d 1d 11 d1d0

Input Table for JK

| Input | Table | for | J |

|-------|-------|-----|---|

$y_1y_2$

00

01

10

11

Х

0 | 1

d

0 1

d

1 1

d d Input Table for K

|          | 2 | Κ |

|----------|---|---|

| $y_1y_2$ | 0 | 1 |

| 00       | d | d |

| 01       | 1 | 0 |

| 10       | d | d |

| 11       | 1 | 0 |

## Flip-Flop Characteristic Tables

| Q(t) | SR | Q(t+1) |

|------|----|--------|

| 0    | 00 | 0      |

| 0    | 01 | 0      |

| 0    | 10 | 1      |

| 0    | 11 |        |

| 1    | 00 | 1      |

| 1    | 01 | 0      |

| 1    | 10 | 1      |

| 1    | 11 |        |

| Q(t) | JK | Q(t+1) |

|------|----|--------|

| 0    | 00 | 0      |

| 0    | 01 | 0      |

| 0    | 10 | 1      |

| 0    | 11 | 1      |

| 1    | 00 | 1      |

| 1    | 01 | 0      |

| 1    | 10 | 1      |

| 1    | 11 | 0      |

| Q(t) | D | Q(t+1) |

|------|---|--------|

| 0    | 0 | 0      |

| 0    | 1 | 1      |

| 1    | 0 | 0      |

| 1    | 1 | 1      |

| Q(t) | T | Q(t+1) |

|------|---|--------|

| 0    | 0 | 0      |

| 0    | 1 | 1      |

| 1    | 0 | 1      |

| 1    | 1 | 0      |

## Flip-Flop Excitation Tables

| Q(t) | Q(t+1) | SR | D | JK | T |

|------|--------|----|---|----|---|

| 0    | 0      | 0d | 0 | 0d | 0 |

| 0    | 1      | 10 | 1 | 1d | 1 |

| 1    | 0      | 01 | 0 | d1 | 1 |

| 1    | 1      | d0 | 1 | d0 | 0 |